# GT-64111 System Controller for RC4640,

RM523X and VR4300 CPUs

Product Preview Revision 1.1 FEB 4, 1999

Please contact Galileo Technology for possible updates before finalizing a design.

## FEATURES

Integrated PCI system controller for high-performance cost sensitive embedded applications

- Support the following 32-bit bus CPUs:

- IDT RC4640 and RC4650 (in 32-bit mode) QED RM523X

- NEC/Toshiba VR4300

- Up to 66MHz CPU bus frequency

- 64 byte CPU write posting buffer

- 32-bit wide, 16 levels deep

Accepts CPU writes with zero wait-states

- EDO and Fast Page Mode DRAM controller

- 512MB address space

- Supports DRAM bank interleaving -

- 256KB-16MB device depth

- 1-4 banks supported

- 32-bit or 64-bit data width

- Parity supported

- Zero wait-state interleaved burst accesses at

- 66MHz

- Device controller

- 5 chip selects

- Programmable timing for each chip select

- Supports many types of standard memory and I/O devices

- Up to 160MB address space

- Optional external wait-state support

- 8-,16-,32- and 64-bit width device support

- Support for boot ROMs

- Parity supported for devices

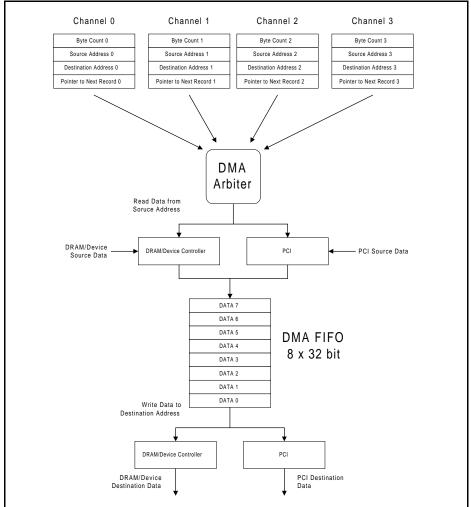

- Four channel DMA controller

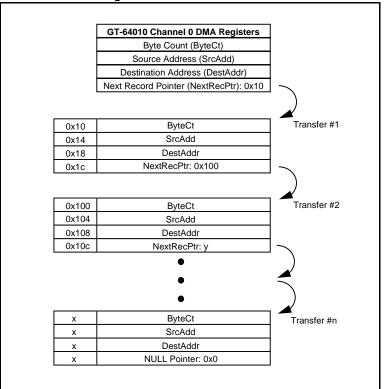

- Chaining via linked-lists of records

- Byte alignment on source and destination

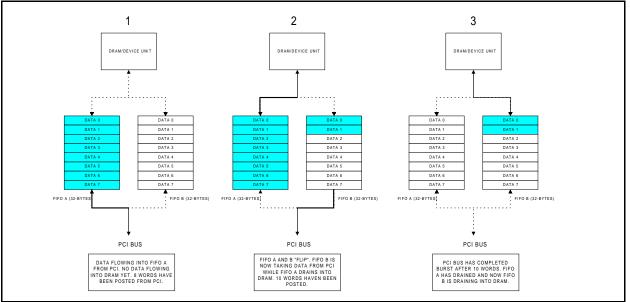

- Transfers through 32-byte internal FIFO

- Moves data between PCI, memory, and devices

- High-performance 32-bit Universal PCI 2.1 interface

- - 96-bytes of posted write and read prefetch buffers

- 32-bit PCI master and target operations

- PCI bus speed of up to 66MHz with no wait states

- Operates either synchronous or asynchronous to CPU clock

- Burst transfers used for efficient data movement

- Doorbell interrupts provided between CPU and PCI -Supports flexible byte swapping through PCI interface

- Synchronization barrier support

- PCI configuration registers can be accessed from both CPU and PCI side

- Support for both 5V and 3.3V operation

- Host to PCI bridge

- Translates CPU cycles into PCI I/O or Memory cycles

- Generates PCI Configuration, Interrupt Acknowledge, and Special cycles on PCI bus

- PCI to Main Memory bridge

- Supports fast back-to-back transactions

- Supports memory and I/O transactions to internal

- configuration registers

- Supports locked operations

- Three 24-bit wide and one 32-bit wide timer/counters

- Plug and Play Support

- PC compatible configuration registers

- PCI configuration header can be loaded from boot PROM

- PCI configuration registers are accessed from both CPU and PCI bus

- 3.3V Supply Voltage (PCI and Peripherals) - 5V tolerant I/Os

- 208 PQFP

2

## **Table of Contents**

| 1. | ٥V  | ERVIEW                                                    | 7 |

|----|-----|-----------------------------------------------------------|---|

|    | 1.1 | CPU bus Interface                                         | 7 |

|    | 1.2 | DRAM and Device Interface                                 | 7 |

|    | 1.3 | PCI Interface.                                            | 7 |

|    | 1.4 | DMA Engines                                               | 8 |

|    | 1.5 | CPUs Supported.                                           |   |

|    | 1.6 | Block Diagram                                             |   |

|    |     |                                                           | _ |

| 2. |     | Information1                                              |   |

|    | 2.1 | Logic Symbol                                              |   |

|    | 2.2 | Pin Assignment Table                                      | 1 |

| 3. | CPU | I/Local Master Interface1                                 | 5 |

| 0. | 3.1 | CPU/Local Master Interface Signals                        |   |

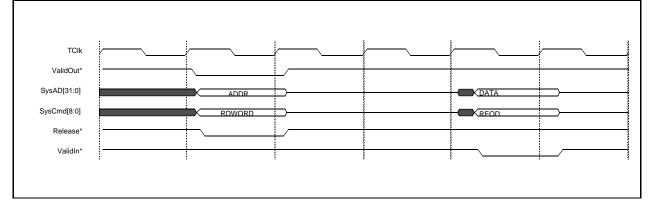

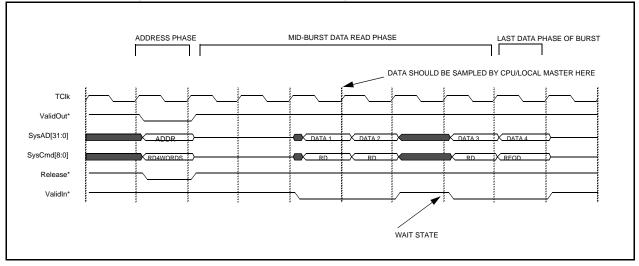

|    | 3.2 | SysAD and SysCmd Buses (9-bit SysCmd Mode)1               |   |

|    | 0.2 | 3.2.1 SysAD Read Protocol                                 |   |

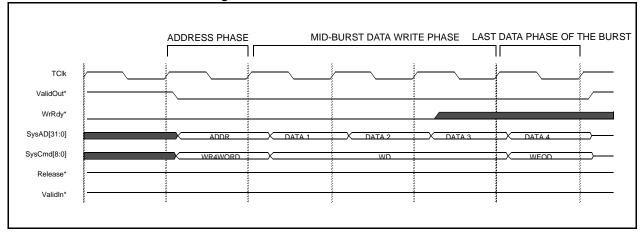

|    |     | 3.2.2 SysAD Write Protocol                                |   |

|    | 3.3 | 4300 Bus Mode Support (5-bit SysCmd Mode)1                |   |

|    | 3.4 | Operation of WrRdy* and the Internal Write Posting Queues |   |

|    | 3.5 | MIPs Write Modes and Write Patterns Supported             |   |

|    | 3.6 | CPU/Local Master Interface Endianess                      |   |

|    | 3.7 | Burst Order                                               |   |

|    | 3.8 | CPU/Local Master Interface Restrictions                   |   |

|    |     |                                                           |   |

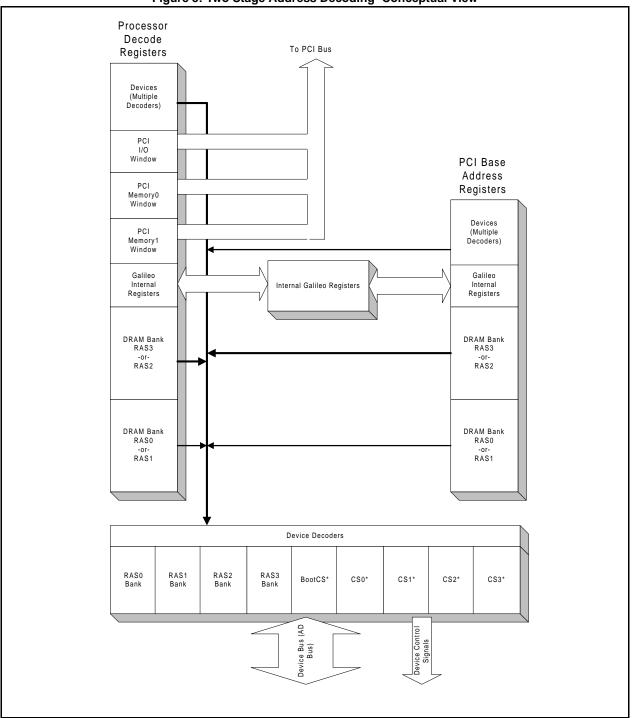

| 4. | Add | ress Space Decoding2                                      |   |

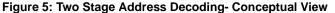

|    | 4.1 | Two Stage Decoding Process                                |   |

|    |     | 4.1.1 CPU/Local Master Side Decoding Process              |   |

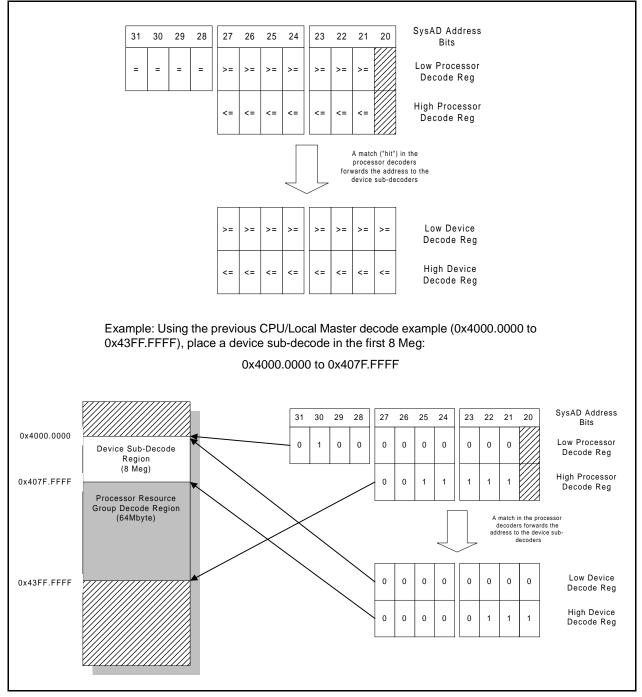

|    | 4.2 | PCI Side Decoding Process                                 |   |

|    | 4.3 | Disabling the Device Decoders                             |   |

|    | 4.4 | DMA Unit Address Decoding                                 |   |

|    | 4.5 | Address Space Decoding Errors                             |   |

|    | 4.6 | Default Memory Map                                        | 9 |

| 5. | Mon | nory Controller                                           | 1 |

| J. | 5.1 | DRAM Controller                                           |   |

|    | 5.1 | 5.1.1 DRAM Refresh                                        |   |

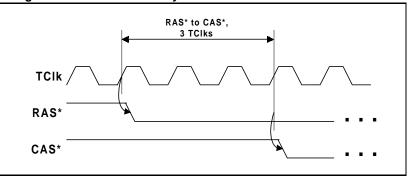

|    |     | 5.1.2 Assymetrically RAS*/CAS* Addressing                 |   |

|    |     | 5.1.3 DAdr[11]/ADS* Function                              |   |

|    |     | 5.1.4 Programmable DRAM Timing Parameters                 |   |

|    |     | 5.1.5 DRAM Bank Width and Location                        |   |

|    |     | 5.1.6 DRAM Performance                                    |   |

|    | 5.2 | Device Controller                                         |   |

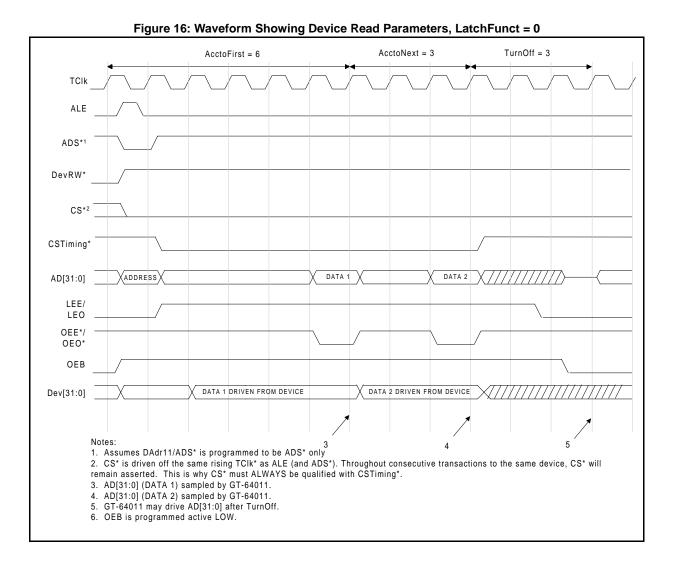

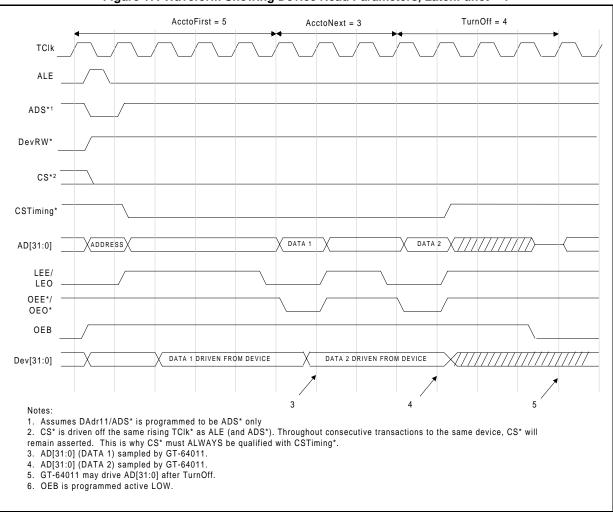

|    | 0.2 | 5.2.1 TurnOff, bits [2:0]                                 |   |

|    |     | 5.2.2 AccToFirst, bits [6:3]                              |   |

|    |     | 5.2.3 AccToNext, bits [10:7]                              |   |

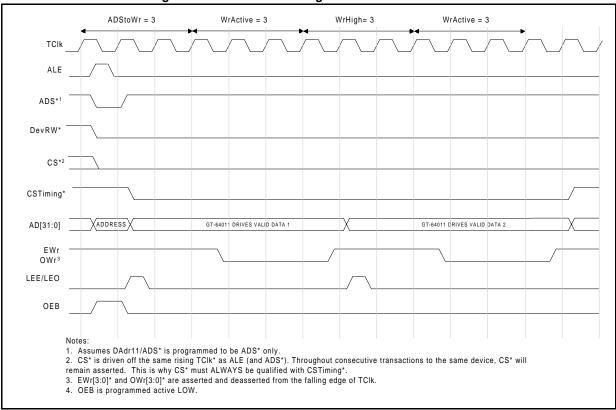

|    |     | 5.2.4 ADStoWr, bits[13:11]                                |   |

|    |     | 5.2.5 WrActive, bits[16:14]                               |   |

|    |     | 5.2.6 WrHigh, bits[19:17]                                 |   |

|    |     | 5.2.7 Burst Transactions                                  |   |

|    |     | 5.2.8 Packing and Unpacking Data and Burst Support        |   |

|    |     | 5.2.9 "Destructive" Reads                                 |   |

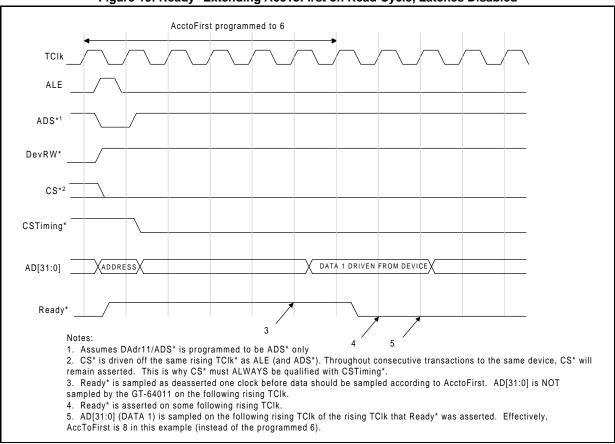

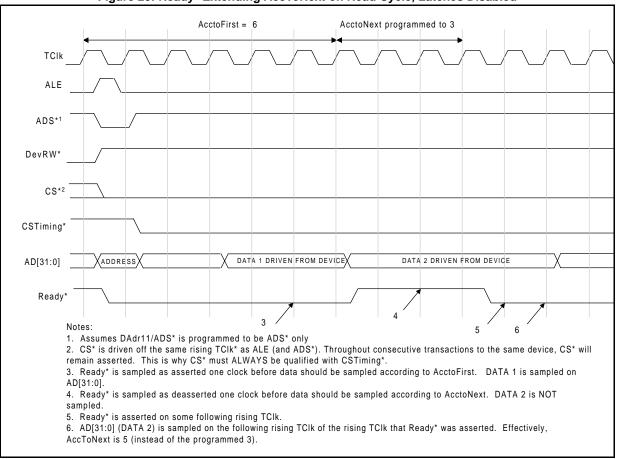

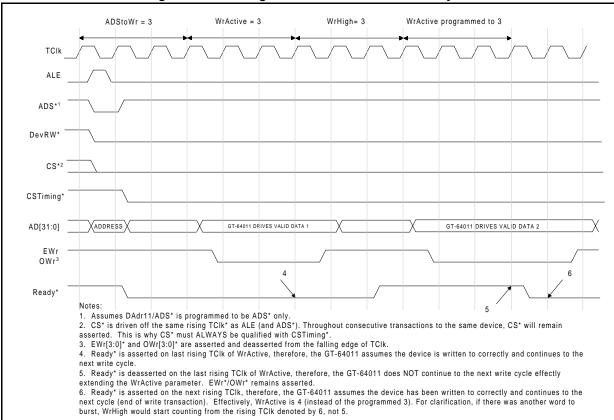

|    |     | 5.2.10 Ready* Support                                     |   |

|    |     | 5.2.11 Device Bank Width and Location                     |   |

|    |     |                                                           | - |

4

|            |            | 5.2.12 SysAD to AD Addressing.                                               | 13  |

|------------|------------|------------------------------------------------------------------------------|-----|

|            | 5.3        | Data Latches                                                                 |     |

|            | 5.5        |                                                                              |     |

|            | <b>Г</b> 4 |                                                                              |     |

|            | 5.4        | Parity Checking Support                                                      |     |

|            | 5.5        | Addressing                                                                   |     |

|            | 5.6        | Memory Interface Restrictions                                                | 45  |

| 6.         | PCU        | Bus                                                                          | 17  |

| 0.         | 6.1        | PCI Master Operation                                                         |     |

|            | 0.1        | 6.1.1 PCI Master CPU/Local Master Address Space Decode and Translation       |     |

|            |            | 6.1.2 PCI Master CPU/Local Master Byte Swapping                              |     |

|            |            | 6.1.3 PCI Master FIFOs                                                       |     |

|            |            | 6.1.4 PCI Master DMA                                                         |     |

|            |            | 6.1.5 PCI Master RETRY Counter                                               |     |

|            |            |                                                                              |     |

|            | ~ ~        | 6.1.6 Cache Line Size.                                                       |     |

|            | 6.2        | PCI Target Interface                                                         |     |

|            |            | 6.2.1 PCI Target FIFOs                                                       |     |

|            |            | 6.2.2 PCI Target Address Space Decode and Byte Swapping.                     |     |

|            |            | 6.2.3 Tweaking the Performance of the Target Interface                       |     |

|            | 6.3        | PCI Synchronization Barriers                                                 |     |

|            | 6.4        | PCI Master Configuration                                                     |     |

|            |            | 6.4.1 Special Cycles and Interrupt Acknowledge                               |     |

|            | 6.5        | Target Configuration and Plug and Play                                       |     |

|            |            | 6.5.1 Plug and Play Base Address Register Sizing                             |     |

|            |            | 6.5.2 Multi-Function Device, Swap BARs.                                      |     |

|            |            | 6.5.3 PCI Autoconfiguration at RESET.                                        |     |

|            |            | 6.5.4 Expansion ROM Functionality                                            |     |

|            | 6.6        | PCI Parity Support                                                           |     |

|            | 6.7        | PCI Bus/Device Bus/CPU/Local Master Clock Synchronization                    |     |

|            | 6.8        | 66MHz Capability Bit                                                         |     |

|            | 6.9        | Universal PCI Vio Pin                                                        |     |

|            | 6.10       | PCI Interface Restrictions                                                   |     |

|            |            | 6.10.1 Master                                                                |     |

|            |            | 6.10.2 Slave                                                                 |     |

|            |            | 6.10.3 Master and Slave.                                                     | .55 |

| 7.         | рма        | Controller                                                                   | 56  |

| <i>'</i> . | 7.1        | DMA Channel Registers                                                        |     |

|            | 7.1        | DMA Channel Control Register (0x840 - 0x84c).                                |     |

|            | 1.2        | 7.2.1 AddControl[1:0], GT-64111-P-1 ONLY                                     |     |

|            |            | 7.2.1 AddControl[1.0], G1-64111-F-1 ONL1                                     |     |

|            |            | 7.2.2 StcDir, bits[5:2]                                                      |     |

|            |            | 7.2.3 DesiDii, bits[5.4]                                                     |     |

|            |            | 7.2.4         Dat marshim, bits[0.0]           7.2.5         ChainMod, bit 9 |     |

|            |            |                                                                              |     |

|            |            |                                                                              |     |

|            |            | 7.2.7 TransMod, bit 11                                                       |     |

|            |            | 7.2.8         ChanEn, bit 12           7.2.9         FetNexRec, bit 13       |     |

|            |            |                                                                              |     |

|            | 70         | 7.2.10 DMAActSt, bit 14 (Read Only).                                         |     |

|            | 7.3        | Restarting a Disabled Channel (previously active)                            |     |

|            | 7.4        | Reprogramming an Active Channel                                              |     |

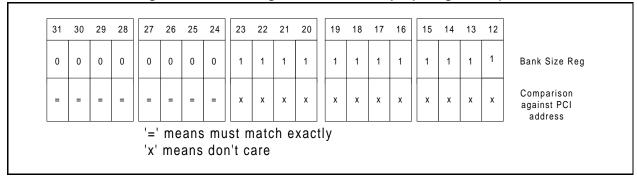

|            | 7.5        | Arbitration                                                                  |     |

|            | 7.6<br>7.7 | DMAReq[3:0]*                                                                 |     |

|            | 7.7        | DMAAck[3:0]*                                                                 |     |

|            | 7.8        | Design Information                                                           |     |

|            |            | 7.8.1 DMA in Demand Mode                                                     | 64  |

#

## GT-64111 System Controller for RC4640, RM523X and VR4300 CPUs

|     | <ul> <li>7.8.2 DMA in Block Mode</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 62<br>62<br>62<br>62                                                                                                                                                 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8.  | Timer/Counters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                      |

| 9.  | Interrupt Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 65                                                                                                                                                                   |

| 10. | Reset Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                      |

| 11. | Connecting the Memory Controller to DRAM and Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                      |

|     | 11.1       Working Without Data Latches         11.2       Working With Data Latches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                      |

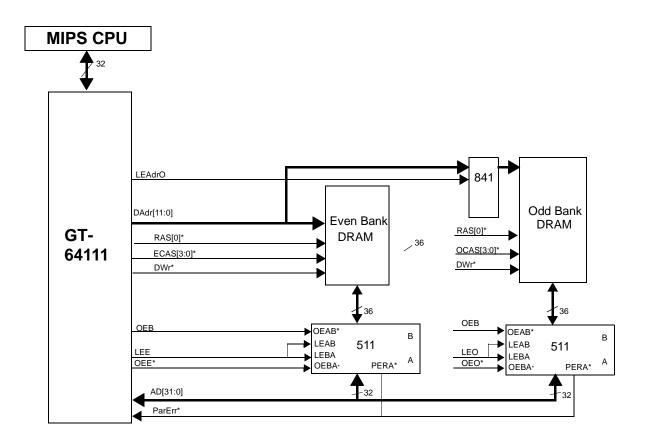

|     | 11.2.1 64-bit DRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                      |

|     | 11.2.2 32-bit DRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                      |

|     | 11.2.3       64-bit Devices         11.2.4       32-bit or Less Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                      |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                      |

| 12. | Big and Little Endian           12.1 Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                      |

|     | 12.11 Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                      |

|     | 12.1.2 Bit 0 of the PCI Internal Command register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 74                                                                                                                                                                   |

|     | 12.2 Configuring a System for Big and Little Endian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 74                                                                                                                                                                   |

| 13. | Using the GT-64111 Without the CPU/Local Master Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 76                                                                                                                                                                   |

| 14. | Using the GT-64111 Without the PCI Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 76                                                                                                                                                                   |

|     | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                      |

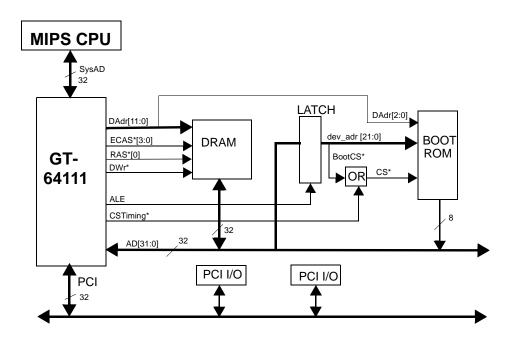

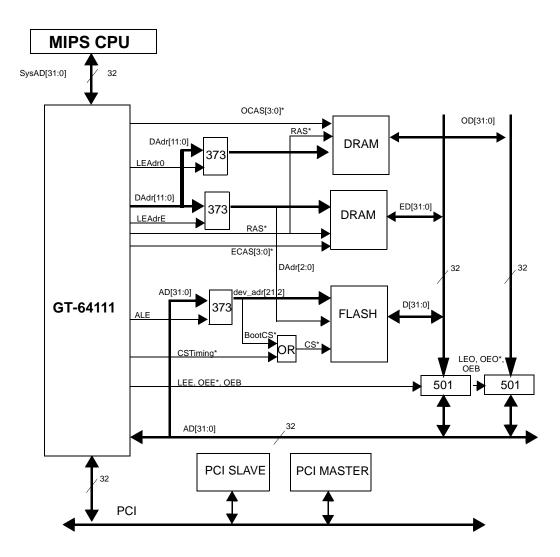

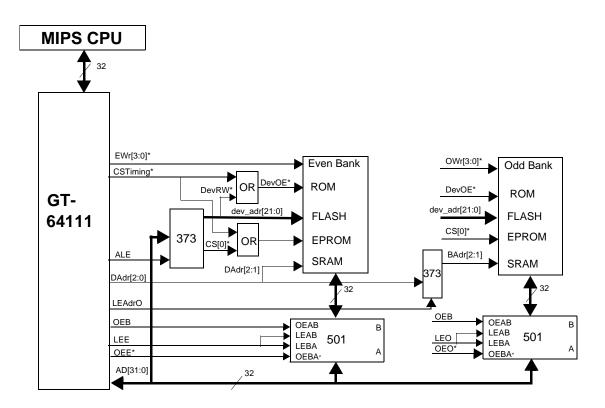

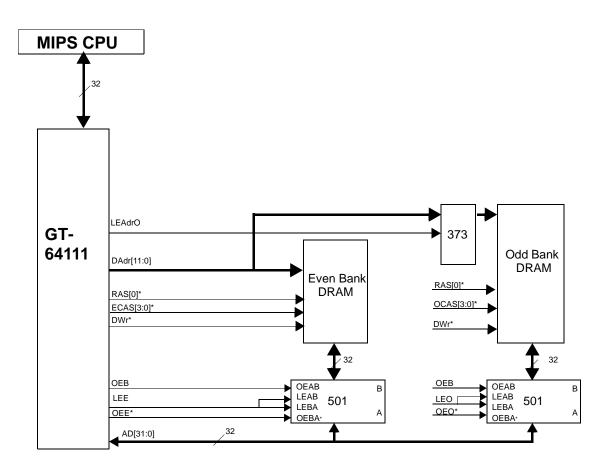

| 15. | APPLICATIONS: SYSTEM CONFIGURATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 77                                                                                                                                                                   |

| 15. | APPLICATIONS: SYSTEM CONFIGURATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>77</b>                                                                                                                                                            |

| 15. | APPLICATIONS: SYSTEM CONFIGURATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>77</b><br>77<br>78                                                                                                                                                |

| 15. | APPLICATIONS: SYSTEM CONFIGURATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>77</b><br>77<br>78<br>79                                                                                                                                          |

| 15. | APPLICATIONS: SYSTEM CONFIGURATIONS         15.1 Minimal System Configuration         15.2 Typical System         15.3 Interface to Asynchronous Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>77</b><br>77<br>78<br>79<br>80                                                                                                                                    |

| 15. | APPLICATIONS: SYSTEM CONFIGURATIONS         15.1       Minimal System Configuration         15.2       Typical System         15.3       Interface to Asynchronous Devices         15.4       Interface to DRAM         15.5       A System With Parity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>77</b><br>77<br>78<br>79<br>80<br>81                                                                                                                              |

| -   | APPLICATIONS: SYSTEM CONFIGURATIONS         15.1       Minimal System Configuration         15.2       Typical System         15.3       Interface to Asynchronous Devices         15.4       Interface to DRAM         15.5       A System With Parity         15.6       Designing for Compatibility with the GT-64011         16.1       Major Hardware Differences Between the GT-64011 and GT-64111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>77</b> 78798081 <b>83</b>                                                                                                                                         |

| -   | APPLICATIONS: SYSTEM CONFIGURATIONS          15.1       Minimal System Configuration         15.2       Typical System         15.3       Interface to Asynchronous Devices         15.4       Interface to DRAM         15.5       A System With Parity         Designing for Compatibility with the GT-64011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>77</b> 78798081 <b>83</b>                                                                                                                                         |

| -   | APPLICATIONS: SYSTEM CONFIGURATIONS         15.1       Minimal System Configuration         15.2       Typical System         15.3       Interface to Asynchronous Devices         15.4       Interface to DRAM         15.5       A System With Parity         16.1       Major Hardware Differences Between the GT-64011 and GT-64111         16.2       All Differences Between the GT-64011 and GT-64111         REGISTER TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                      |

| 16. | APPLICATIONS: SYSTEM CONFIGURATIONS         15.1       Minimal System Configuration         15.2       Typical System         15.3       Interface to Asynchronous Devices         15.4       Interface to DRAM         15.5       A System With Parity         16.1       Major Hardware Differences Between the GT-64011         16.2       All Differences Between the GT-64011 and GT-64111         16.2       All Differences Between the GT-64011 and GT-64111         17.1       Access to On-Chip PCI Configuration Space Registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                      |

| 16. | APPLICATIONS: SYSTEM CONFIGURATIONS         15.1       Minimal System Configuration         15.2       Typical System         15.3       Interface to Asynchronous Devices         15.4       Interface to DRAM         15.5       A System With Parity         Designing for Compatibility with the GT-64011         16.1       Major Hardware Differences Between the GT-64011 and GT-64111         16.2       All Differences Between the GT-64011 and GT-64111         16.2       All Differences Between the GT-64011 and GT-64111         17.1       Access to On-Chip PCI Configuration Space Registers.         17.2       Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                      |

| 16. | APPLICATIONS: SYSTEM CONFIGURATIONS         15.1       Minimal System Configuration         15.2       Typical System         15.3       Interface to Asynchronous Devices         15.4       Interface to DRAM         15.5       A System With Parity         16.1       Major Hardware Differences Between the GT-64011         16.2       All Differences Between the GT-64011 and GT-64111         16.2       All Differences Between the GT-64011 and GT-64111         17.1       Access to On-Chip PCI Configuration Space Registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                      |

| 16. | APPLICATIONS: SYSTEM CONFIGURATIONS         15.1       Minimal System Configuration         15.2       Typical System         15.3       Interface to Asynchronous Devices         15.4       Interface to DRAM         15.5       A System With Parity         Designing for Compatibility with the GT-64011         16.1       Major Hardware Differences Between the GT-64011 and GT-64111         16.2       All Differences Between the GT-64011 and GT-64111         16.2       All Differences Between the GT-64011 and GT-64111         16.2       All Differences Detween the GT-64011 and GT-64111         17.1       Access to On-Chip PCI Configuration Space Registers         17.2       Register Map         17.3       CPU/Local Master Interface         17.4       CPU/Local Master Decode         17.5       Device Decode                                                                                                                                                                                                                                                                                    | <b>77</b><br>78<br>79<br>80<br>81<br><b>83</b><br><b>83</b><br><b>83</b><br><b>83</b><br><b>85</b><br><b>85</b><br><b>85</b><br><b>85</b><br><b>90</b><br>90<br>     |

| 16. | APPLICATIONS: SYSTEM CONFIGURATIONS         15.1       Minimal System Configuration         15.2       Typical System         15.3       Interface to Asynchronous Devices         15.4       Interface to DRAM         15.5       A System With Parity         Designing for Compatibility with the GT-64011         16.1       Major Hardware Differences Between the GT-64011 and GT-64111         16.2       All Differences Between the GT-64011 and GT-64111         16.2       All Differences Between the GT-64011 and GT-64111         17.1       Access to On-Chip PCI Configuration Space Registers         17.3       CPU/Local Master Interface         17.4       CPU/Local Master Decode         17.5       Device Decode         17.6       DRAM Configuration                                                                                                                                                                                                                                                                                                                                                   | <b>77</b><br>78<br>79<br>80<br>81<br>83<br>83<br>83<br>83<br>85<br>85<br>85<br>90<br>90<br>93<br>96                                                                  |

| 16. | APPLICATIONS: SYSTEM CONFIGURATIONS         15.1       Minimal System Configuration         15.2       Typical System         15.3       Interface to Asynchronous Devices         15.4       Interface to DRAM         15.5       A System With Parity         Designing for Compatibility with the GT-64011         16.1       Major Hardware Differences Between the GT-64011 and GT-64111         16.2       All Differences Between the GT-64011 and GT-64111         16.2       All Differences Between the GT-64011 and GT-64111         16.2       All Differences Detween the GT-64011 and GT-64111         17.1       Access to On-Chip PCI Configuration Space Registers         17.2       Register Map         17.3       CPU/Local Master Interface         17.4       CPU/Local Master Decode         17.5       Device Decode                                                                                                                                                                                                                                                                                    |                                                                                                                                                                      |

| 16. | APPLICATIONS: SYSTEM CONFIGURATIONS         15.1       Minimal System Configuration         15.2       Typical System         15.3       Interface to Asynchronous Devices         15.4       Interface to DRAM         15.5       A System With Parity         Designing for Compatibility with the GT-64011         16.1       Major Hardware Differences Between the GT-64011 and GT-64111         16.2       All Differences Between the GT-64011 and GT-64111         16.2       All Differences Between the GT-64011 and GT-64111         16.2       All Differences Between the GT-64011 and GT-64111         17.4       Cregister TABLES         17.1       Access to On-Chip PCI Configuration Space Registers         17.2       Register Map         17.3       CPU/Local Master Interface         17.4       CPU/Local Master Decode         17.5       Device Decode         17.6       DRAM Configuration         17.7       DRAM Parameters         17.8       Device Parameters         17.9       DMA Record                                                                                                    |                                                                                                                                                                      |

| 16. | APPLICATIONS: SYSTEM CONFIGURATIONS         15.1       Minimal System Configuration         15.2       Typical System         15.3       Interface to Asynchronous Devices         15.4       Interface to DRAM         15.5       A System With Parity         Designing for Compatibility with the GT-64011         16.1       Major Hardware Differences Between the GT-64011 and GT-64111         16.2       All Differences Between the GT-64011 and GT-64111         16.2       All Differences Between the GT-64011 and GT-64111         16.2       All Differences Between the GT-64011 and GT-64111         17.4       CPULCacl Master Interface         17.3       CPU/Local Master Interface         17.4       CPU/Local Master Decode         17.5       Device Decode         17.6       DRAM Configuration         17.7       DRAM Configuration         17.7       DRAM Configuration         17.7       DRAM Parameters         17.8       Device Parameters         17.9       DMA Record         17.10       DMA Channel Control                                                                              |                                                                                                                                                                      |

| 16. | APPLICATIONS: SYSTEM CONFIGURATIONS         15.1         Minimal System Configuration         15.2       Typical System         15.3       Interface to Asynchronous Devices         15.4       Interface to DRAM         15.5       A System With Parity         Designing for Compatibility with the GT-64011         16.1       Major Hardware Differences Between the GT-64011 and GT-64111         16.2       All Differences Between the GT-64011 and GT-64111         16.2       All Differences Between the GT-64011 and GT-64111         17.4       Access to On-Chip PCI Configuration Space Registers         17.3       CPU/Local Master Interface         17.4       CPU/Local Master Decode         17.5       Device Decode         17.6       DRAM Configuration         17.7       DRAM Configuration         17.7       DRAM Parameters         17.8       Device Parameters         17.9       DMA Record         17.10 DMA Channel Control.       17.11 Arbiter Control, Offset: 0x860                                                                                                                       |                                                                                                                                                                      |

| 16. | APPLICATIONS: SYSTEM CONFIGURATIONS         15.1       Minimal System Configuration         15.2       Typical System         15.3       Interface to Asynchronous Devices         15.4       Interface to DRAM         15.5       A System With Parity         Designing for Compatibility with the GT-64011         16.1       Major Hardware Differences Between the GT-64011 and GT-64111         16.2       All Differences Between the GT-64011 and GT-64111         16.2       All Differences Between the GT-64011 and GT-64111         16.2       All Differences Between the GT-64011 and GT-64111         17.4       CPULCacl Master Interface         17.3       CPU/Local Master Interface         17.4       CPU/Local Master Decode         17.5       Device Decode         17.6       DRAM Configuration         17.7       DRAM Configuration         17.7       DRAM Configuration         17.7       DRAM Parameters         17.8       Device Parameters         17.9       DMA Record         17.10       DMA Channel Control                                                                              | <b>77</b><br>78<br>79<br>80<br>81<br><b>83</b><br>83<br>83<br>83<br>83<br>85<br>85<br>85<br>90<br>90<br>90<br>96<br>96<br>98<br>99<br>99<br>99<br>99<br>99<br>99<br> |

| 16. | APPLICATIONS: SYSTEM CONFIGURATIONS         15.1         Minimal System Configuration         15.2         Typical System         15.3         15.4         Interface to Asynchronous Devices         15.4         15.5         A System With Parity         Designing for Compatibility with the GT-64011         16.1         Major Hardware Differences Between the GT-64011 and GT-64111         16.2         All Differences Between the GT-64011 and GT-64111         Register Map         17.1         Access to On-Chip PCI Configuration Space Registers         17.3       CPU/Local Master Interface         17.4       CPU/Local Master Decode         17.5       Device Decode         17.6       DRAM Configuration         17.7       DRAM Parameters         17.9       DMA Record         17.10 DMA Channel Control | <b>77</b><br>78<br>79<br>80<br>81<br><b>83</b><br>83<br>83<br>83<br>83<br>85<br>85<br>90<br>90<br>90<br>90<br>93<br>96<br>98<br>99<br>99<br>99<br>99<br>99<br>99<br> |

## GT-64111 System Controller for RC4640, RM523X and VR4300 CPUs

| 18. | PINOUT TABLE, 208 pin PQFP (sorted by number)1                                                                                                                                                                                                                                                   | 17               |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 19. | DC CHARACTERISTICS - PRELIMINARY/SUBJECT TO CHANGE       1         19.1       Absolute Maximum Ratings       1         19.2       Recommended Operating Conditions       1         19.3       DC Electrical Characteristics Over Operating Range       1         19.4       Thermal Data       1 | 19<br> 19<br> 19 |

| 20. | AC TIMING - TARGETS/SUBJECT TO CHANGE                                                                                                                                                                                                                                                            |                  |

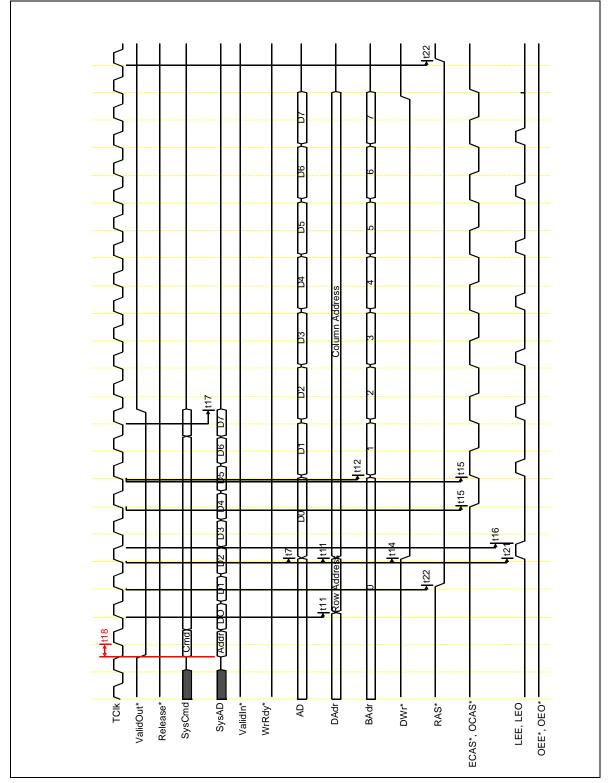

| 21. | Functional Waveforms1                                                                                                                                                                                                                                                                            | 28               |

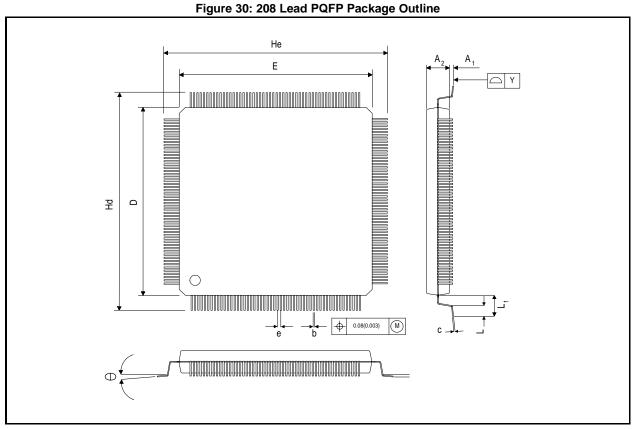

| 22. | Packaging1                                                                                                                                                                                                                                                                                       | 29               |

| 23. | Revision History1                                                                                                                                                                                                                                                                                | 30               |

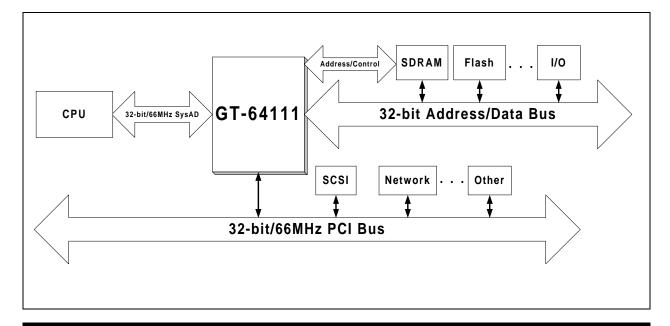

## 1. OVERVIEW

The GT-64111 provides a single-chip solution for designers building systems around 32-bit bus/64-bit internal MIPS embedded processors. The architecture of the GT-64111 supports several system implementations for different applications and cost/performance points. It is possible to design a powerful system with minimal glue logic, or add commodity logic (controlled by the GT-64111) for differentiated system architectures that attain higher performance.

The GT-64111 has a three bus architecture:

- A 32-bit interface to the CPU bus (SysAD bus)

- A 32-bit interface to the memory and device subsystem.

- A 32-bit interface to the PCI bus.

The three buses are de-coupled from each other in most accesses, enabling concurrent operation of the CPU bus, PCI devices, and accesses to memory. For example, the CPU bus can write to the on-chip write buffer, a DMA agent can move data from DRAM to its own buffers, and a PCI device can write into an on-chip FIFO, all simultaneously.

#### 1.1 CPU bus Interface

The GT-64111 SysAD bus allows the CPU and other local bus masters to access the PCI and memory/device buses. The SysAD bus protocol supports byte and 32-bit word operations with burst lengths up to 8 words (sub-word, 2 word, and 4 word transfers are also supported.) With a maximum frequency of 66MHz, the CPU can transfer in excess of 150 Mbytes/sec.

The GT-64111 can automatically determine if the attached MIPS processor is using the 8-bit SysCmd protocol (RC4640, RM523X) or the 5-bit SysCmd protocol (VR4300).

#### **1.2 DRAM and Device Interface**

The GT-64111 has a flexible DRAM controller that supports EDO as well as standard page mode DRAMs. With 45ns standard DRAMs, the GT-64111 can return data at 8-2-2-2-2-2-2<sup>1</sup> clocks with 32-bit DRAMs and at 8-1-1-1-1-1 clocks with 64-bit interleaved DRAMs to the CPU bus- at 66Mhz local bus speed. (In "wait-state" nomenclature this equates to 5-1-1-1-1-1-1 and 5-0-0-0-0-0-0.) The DRAM controller supports different depth devices in each bank.

NOTE: The performance acheived in interleave mode is equivalent to that possible with SDRAM. Furthermore, EDO does not have the granularity/memory waste issues associated with SDRAM (i.e. it is easy to build the smaller arrays required in many systems.)

The GT-64111 memory controller supports different types of memory and I/O devices. It has the control signals and the timing programmability to support devices such as Flash, EPROMs, SRAMs, FIFOs, and I/O controllers. Device widths from 8-bits to 64-bits are supported.

Parity generation and checking is supported externally and is optional for each bank of DRAM or any other device on the memory bus.

## 1.3 PCI Interface

The GT-64111 interfaces directly with the PCI bus. The GT-64111 can be either a master initiating a PCI bus operation, or a target responding to a PCI bus operation. The GT-64111 incorporates 96-bytes of posted write and read prefetch buffers for efficient data transfer between the CPU bus/DMA to PCI, and PCI to main memory.

The GT-64111 becomes a PCI bus master when the CPU bus or the internal DMA engine initiates a bus cycle to a PCI device. The following PCI bus cycles are supported: Memory Read/Write, Interrupt Acknowledge, Special, I/O Read/ Write, or Configuration Read/Write.

The GT-64111 acts as a target when a PCI device initiates a memory access (or an I/O access in the case of internal registers). It responds to all memory read/write accesses, as well as to all configuration and I/O cycles in the case of internal registers.

The GT-64111 contains the required PCI configuration registers. All internal registers, including the PCI configuration

<sup>1.</sup> Note that Galileo uses "total clock" nomenclature and not "wait-state" nomenclature. This means that 8-1-1-1... means 8 clocks to the first data, 1 clock for each additional data (zero wait-states).

#

registers, can be accessed from both the CPU bus and the PCI bus. The GT-64111 configuration register set is PC Plug and Play compatible.

The PCI interface can operate up to 66MHz and is Universal PCI compatible (3.3V/5V).

## 1.4 DMA Engines

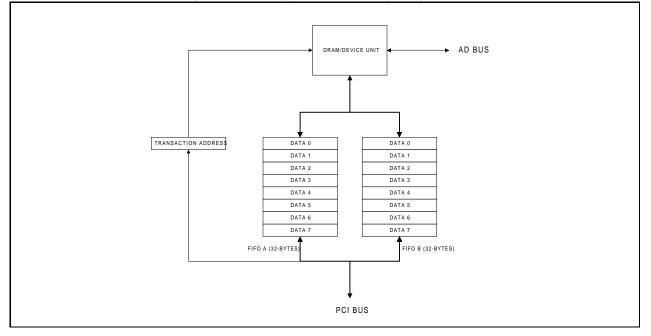

The GT-64111 incorporates four high performance DMA engines. Each DMA engine has the capability to transfer data between PCI devices, between PCI devices and main memory, or between devices residing on the device/memory bus. The DMA uses an internal 32-byte FIFO for temporary storage of DMA data. Source and destination addresses can be non-aligned on any byte address boundary. The DMA channels can be programmed by the CPU bus or by PCI masters, or without CPU bus intervention via a linked list of records that is loaded by the DMA controller into the channel's working set when a DMA transaction ends. The DMA supports increment/decrement/hold on source and destination addresses independently.

## 1.5 CPUs Supported

The GT-64111 can be used with the following processors:

- Integrated Device Technology's (www.idt.com) RC4640 and RC4650 (in 32-bit bus mode)

- Quantum Effect Design's (www.qedinc.com) RM523X

- NEC and Toshiba VR4300

#### 1.6 Block Diagram

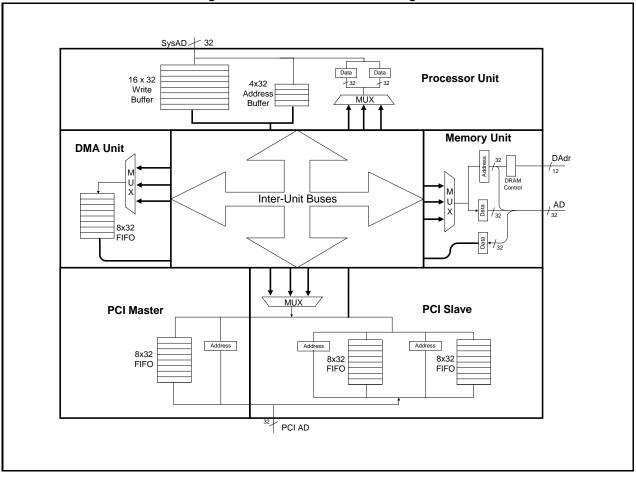

Figure 1, below, shows a simplified block diagram of the GT-64111.

Figure 1: GT-64111 Internal Block Diagram

## 2. Pin Information

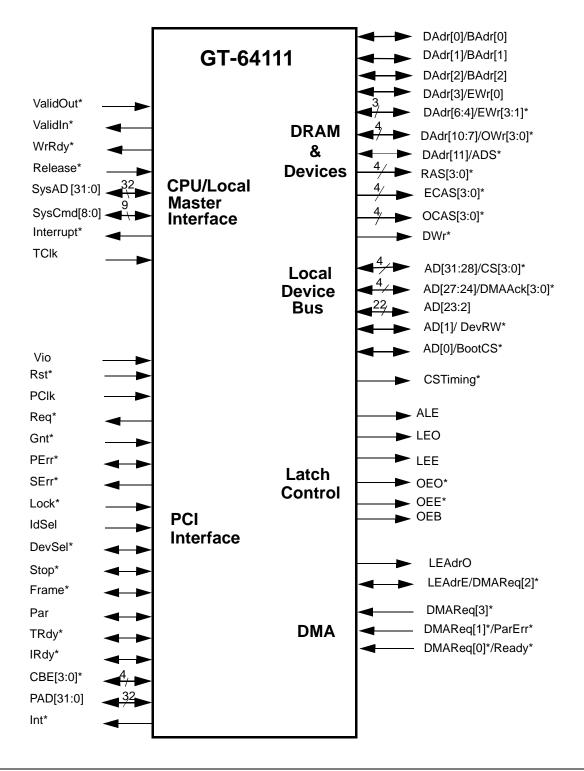

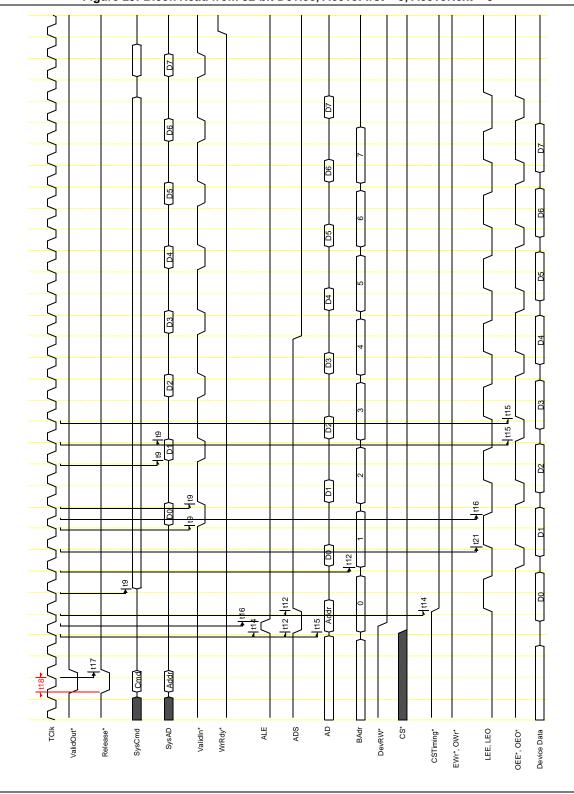

## 2.1 Logic Symbol

## 2.2 Pin Assignment Table

| Pin Name       | I/O        | Description                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|----------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| CPU/Local Mast | er Interfa | ace                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Release*       | I          | <b>Release Interface:</b> Signals to the GT-64111 that the CPU/Local Master has released the SysAD and SysCmd buses for completion of a read request.                                                                                                                                                                                                                  |  |  |  |  |  |

| WrRdy*         | 0          | Write Ready: The GT-64111 signals that it can accept a CPU/Local Master write request (i.e. there is room in the write posting FIFO.)                                                                                                                                                                                                                                  |  |  |  |  |  |

| ValidIn*       | 0          | <b>Valid Input:</b> The GT-64111 signals that it is driving valid data on the SysAD bus, and a valid data identifier on the SysCmd bus.                                                                                                                                                                                                                                |  |  |  |  |  |

| ValidOut*      | I          | Valid Output: Signals that the CPU/Local Master is driving valid address or data on the SysAD bus and a valid command or data identifier on the SysCmd bus.                                                                                                                                                                                                            |  |  |  |  |  |

| SysAD[31:0]    | I/O        | System Address/Data Bus: A 32-bit address and data bus for communication between the CPU/Local Master and GT-64111.                                                                                                                                                                                                                                                    |  |  |  |  |  |

| SysCmd[8:0]    | I/O        | <b>System Command/Data Identifier Bus:</b> A 9-bit bus for command and data identifier transmission between the CPU/Local Master and GT-64111. Only bits SysCmd[4:0] are used when supporting the 4300 bus protocol.                                                                                                                                                   |  |  |  |  |  |

| Interrupt*     | I/O        | <b>Interrupt:</b> An "OR" of all the internal interrupt sources on the GT-64111. This pin is also sampled as an input at reset for configuration purposes.                                                                                                                                                                                                             |  |  |  |  |  |

| TClk           | I          | <b>Clock:</b> The input clock to the GT-64111 (up to 66MHz). TClk is used for both the SysAD and Device interface. TClk must be driven for all applications, including those that do not use the CPU/Local Master bus.                                                                                                                                                 |  |  |  |  |  |

| PCI Interface  |            |                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

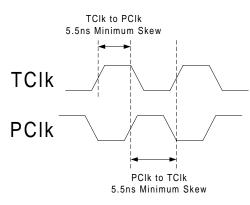

| PClk           | I          | <b>PCI Clock:</b> This pin provides the timing for the PCI transactions. The PCI clock range is between 0 and 66MHz. The PCIk frequency must be lower than TCIk by at least 1 MHz. Please see AC Timing Specifications for more information.                                                                                                                           |  |  |  |  |  |

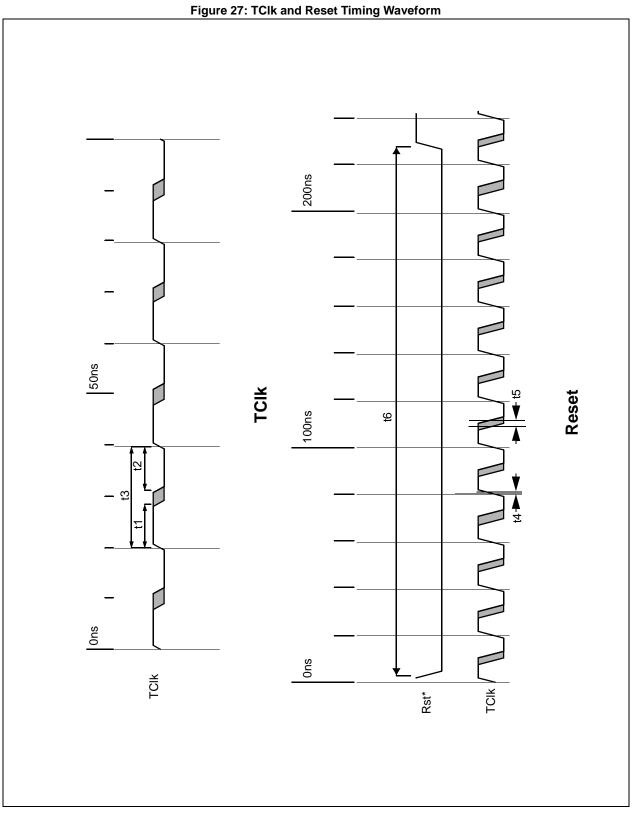

| Rst* I         |            | <b>Reset:</b> Resets the GT-64111 to its initial state. This signal must be asserted for a 10 PCI clock cycles. When in the reset state, all PCI output pins are put into trista all open drain signals are floated.                                                                                                                                                   |  |  |  |  |  |

| PAD[31:0]      | I/O        | <b>PCI Address/Data:</b> 32-bit multiplexed PCI address and data lines. During the first cl of the transaction, PAD[31:0] contains a physical byte address (32 bits). During sub quent clock cycles, PAD[31:0] contains data.                                                                                                                                          |  |  |  |  |  |

| CBE[3:0]*      | I/O        | <b>PCI Bus Command/Byte Enable:</b> During the address phase of the transaction, CBE[3:0]* provide the PCI bus command. During the data phase, these lines provide the byte enables.                                                                                                                                                                                   |  |  |  |  |  |

| Par            | I/O        | <b>Parity:</b> Calculated by the GT-64111 as an even parity bit for the PAD[31:0] and CBE[3:0]* lines.                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Frame* I/O     |            | <b>Frame:</b> Asserted by the GT-64111 to indicate the beginning and duration of a master transaction. Frame* asserts to indicate the beginning of the cycle. While Frame* is asserted, data transfer continues. Frame* deasserts to indicate that the next data phase is the final data phase transaction. Frame* is monitored by the GT-64111 wher acts as a target. |  |  |  |  |  |

| IRdy*          | I/O        | <b>Initiator Ready:</b> Indicates the bus master's ability to complete the current data phase of the transaction. A data phase is completed on any clock when both TRdy* and IRdy* are asserted. Wait cycles are inserted until TRdy* and IRdy* are asserted together.                                                                                                 |  |  |  |  |  |

| TRdy*          | I/O        | <b>Target Ready: Indicates</b> the target agent's ability to complete the current data phase of the transaction. A data phase is completed on any clock when both TRdy* and IRdy* are asserted. Wait cycles are inserted until TRdy* and IRdy* are asserted together.                                                                                                  |  |  |  |  |  |

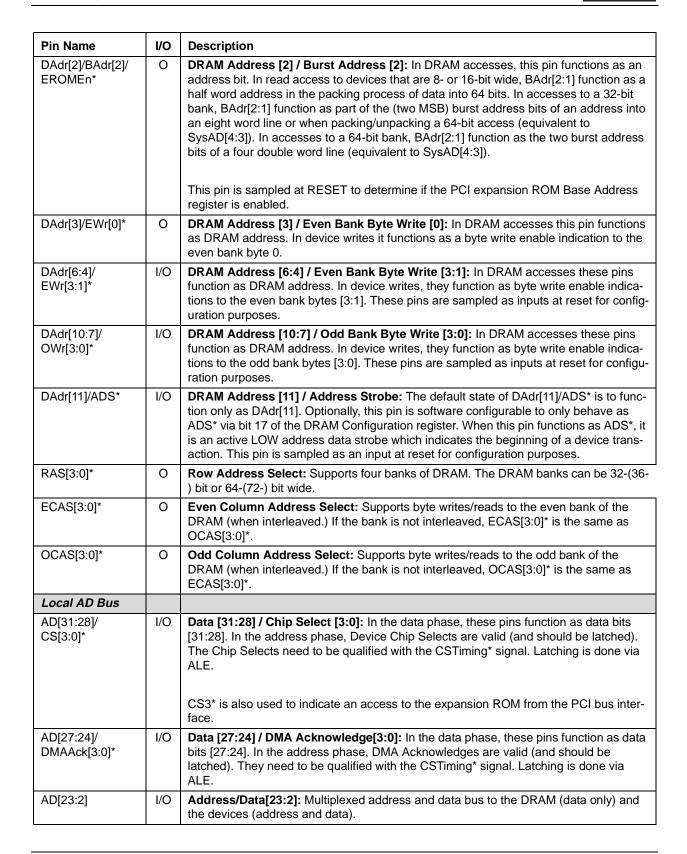

| Pin Name        | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|